# Controlled Charge Transport by Polymer Blend Dielectrics in Top-Gate Organic Field-Effect Transistors for Low-Voltage-Operating **Complementary Circuits**

Kang-Jun Baeg,<sup>†,‡</sup> Dongyoon Khim,<sup>§</sup> Juhwan Kim,<sup>§</sup> Hyun Han,<sup>⊥</sup> Soon-Won Jung,<sup>†</sup> Tae-Wook Kim,<sup>¶</sup> Minji Kang,<sup>§</sup> Antonio Facchetti,<sup>#</sup> Sung-Kyu Hong,<sup>∥</sup> Dong-Yu Kim,<sup>§</sup> and Yong-Young Noh<sup>\*,⊥</sup>

<sup>1</sup>Department of Chemical & Biological Engineering, Hanbat National University, 16-1, Dukmyung-dong, Yuseong-gu, Daejeon 305-719, Republic of Korea

<sup>†</sup>Convergence Components and Materials Research Laboratory, Electronics and Telecommunications Research Institute (ETRI), 218 Gajeongno, Yuseong-gu, Daejeon 305-700, Republic of Korea

<sup>§</sup>Heeger Center for Advanced Materials, School of Materials Science and Engineering, Gwangju Institute of Science and Technology (GIST), 261 Cheomdan-gwagiro, Buk-gu, Gwangju 500-712, Republic of Korea

<sup>#</sup>Polyera Corporation, 8045 Lamon Avenue, Skokie, Illinois 60077, United States

<sup>¶</sup>Korea Institute of Science and Technology (KIST), 864-9, Dunsan-ri, Bongdong-eup, Wan-Ju, Jeonlabukdo 565-902, Republic of Korea

<sup>1</sup>Department of Chemical & Biochemical Engineering, Dongguk University, 3 Pil-dong, Chung-gu, Seoul 100-715, Republic of Korea

ABSTRACT: We report here the development of high-performance p- and nchannel organic field-effect transistors (OFETs) and complementary circuits using inkjet-printed semiconducting layers and high-k polymer dielectric blends of poly(vinylidenefluoride-trifluoroethylene) (P(VDF-TrFE)) and poly(methyl methacrylate) (PMMA). Inkjet-printed p-type polymer semiconductors containing alkylsubstituted thienylenevinylene (TV) and dodecylthiophene (PC12TV12T) and ntype poly{[N,N'-bis(2-octyldodecyl)-naphthalene-1,4,5,8-bis(dicarboximide)-2,6diyl]-alt-5,5'-(2,2'-dithiophene)} (P(NDI2OD-T2)) OFETs typically show high field-effect mobilities ( $\mu_{\text{FET}}$ ) of 0.2–0.5 cm<sup>2</sup>/(V s), and their operation voltage is effectively reduced to below 5 V by the use of P(VDF-TrFE):PMMA blends. The

main interesting result is that the OFET characteristics could be tuned by controlling the mixing ratio of P(VDF-TrFE) to PMMA in the blended dielectric. The  $\mu_{\text{FET}}$  of the PC12TV12T OFETs gradually improves, whereas the P(NDI2OD-T2) OFET properties become slightly worse as the P(VDF-TrFE) content increases. When the mixing ratio is optimized, well-balanced hole and electron mobilities of more than 0.2 cm<sup>2</sup>/(V s) and threshold voltages below  $\pm 3$  V are obtained at a 7:3 ratio of P(VDF-TrFE) to PMMA. Low-voltage-operated (~2 V) printed complementary inverters are successfully demonstrated using the blended dielectric and exhibit an ideal inverting voltage of nearly half of the supplied bias, high voltage gains of greater than 25, and excellent noise margins of more than 75% of the ideal values.

KEYWORDS: organic field effect transistors, polymer dielectric, P(VDF-TrFE), charge transport, conjugated polymers, polymer blend

# INTRODUCTION

Printed electronics have drawn tremendous interest as a new paradigm for the fabrication of large-area, flexible, low-cost optoelectronic and electronic devices such as rollable displays, organic photovoltaics, flash memory, smart sensors, and radio frequency identification (RFID) tags for an item-level tagging.<sup>1-7</sup> Printed electronics are progressing beyond the present level of technology toward more complicated and sophisticated high-end products, such as microprocessors and high-capacity solid-state drives (SSDs). To this end, it is imperative to develop solution-processable functional ink materials for use as high-mobility p- and n-type semiconductors, high-capacitance gate dielectrics, and highly conductive electrodes, as well as higher-resolution and more precise printing processes for sophisticated patterning of semiconductors and electrodes, printing of compatible complementary circuit architectures, etc.<sup>8,9</sup> Solution-processed  $\pi$ -conjugated semiconductive and conductive molecules are the most promising candidate materials for the fabrication of printed and flexible electronics because they have a variety of advantages over their inorganic counterparts including lowtemperature processing, excellent mechanical compatibility attributable to their high bendability and stretchability, and the possibility of fine-tuning the materials' electrical properties through functionalization of these molecules.<sup>10-12</sup> Although remarkable improvement has been achieved in the last two

Received: August 26, 2012 Accepted: October 9, 2012 Published: October 9, 2012

decades, the performance of state-of-the-art printed organic transistors and circuits is still limited by their relatively slow operational speeds of far below 1 MHz.<sup>12–29</sup> Moreover, commonly observed unbalanced characteristics in p- and n-channel OFETs (different mobilities and threshold voltages) make it difficult to develop high-speed complementary printed organic circuitry.<sup>12–29</sup>

The staggered top-gate/bottom-contact (TG/BC) device configuration has many fundamental advantages for OFETs, such as a relatively low contact resistance due to a larger contact area, high environmental stability due to selfencapsulation of the upper gate dielectric and gate electrode, and the ease of down-scaling the source/drain (S/D) channel length by photolithography.<sup>20,21</sup> Moreover, a high-performance TG/BC OFET geometry is quite suitable for high-speed printed integrated circuits (ICs) because of the excellent charge carrier mobility, easy polymer dielectric coating using an orthogonal solvent, and relatively simple overall process for inkjet printing.9 However, the roughness of the top surfaces of printed semiconductor films, which is mainly due to the coffeestain effect resulting from the inkjet printing processes, frequently requires a thicker gate dielectric layer of more than a few hundred nanometers in order to prevent device failures because of a large gate leakage current in TG/BC OFETs.<sup>22,23</sup> Therefore, high-k dielectrics must be used in printed OFETs and circuits to effectively reduce the operating voltage.

Typical high-permittivity (k) polymers, such as poly-(vinylidenefluoride-trifluoroethylene) (P(VDF-TrFE)), have extraordinarily high dielectric constants of more than  $\sim 10$ . However, these polymers have shown strong ferroelectric properties in a crystalline phase which lead to significant bias hysteresis and nonvolatile memory characteristics.<sup>24</sup> Recently, Jung et al. successfully reduced the bias hysteresis and demonstrated low-voltage-operated OFETs using a blend of P(VDF-TrFE) and amorphous polymers such as poly(methyl methacrylate) (PMMA) or poly(vinylidenefluoride) (PVDF) to suppress the formation of the ferroelectric  $\beta$ -phase crystals in the P(VDF-TrFE) thin film.<sup>25,26</sup> Furthermore, the -C-Fdipoles of this high-k dielectric can be used to tune the charge transport in the channel region of TG OFETs through positive charge (hole) accumulation at the semiconductor-dielectric interface.<sup>27</sup> Similar effects of the -C-F dipoles were reported by Kobayashi et al., who used SiO<sub>x</sub> bottom-gate dielectrics modified with fluorinated self-assembled monolayers (SAMs).<sup>28</sup> However, the fluorinated alkyl SAM dielectric can only be used on oxide surfaces.

Here, we report a general methodology for controlling the hole and electron mobility and reducing the operating voltage in TG p- and n-channel OFETs using high-k polymer dielectric blends of P(VDF-TrFE) and PMMA. High-performance, lowvoltage-operated OFETs and complementary inverters were produced using an inkjet-printed p-type polymer semiconductor containing alkyl-substituted thienylenevinylene (TV) and dodecylthiophene (PC12TV12T) and n-type poly{[N,N'-bis(2-octyldodecyl)-naphthalene-1,4,5,8-bis-(dicarboximide)-2,6-diyl]-alt-5,5'-(2,2'-dithiophene)} (P-(NDI2OD-T2)) (ActivInk N2200, Polyera) with the blended polymer dielectric layer. Well-balanced electron and hole mobilities and threshold voltages  $(V_{\rm Th})$  were obtained at a 7:3 blend ratio between P(VDF-TrFE) and PMMA. The optimized p- and n-type printed OFETs showed field-effect mobilities ( $\mu_{\text{FET}}$ ) as high as 0.45 and 0.27 cm<sup>2</sup>/(V s), respectively. It is interesting that the p-type OFET characteristics gradually improved in proportion to the P(VDF-TrFE) concentration in the dielectric blends, while the n-type properties became slightly worse or did not significantly change from those at the optimized blending ratio. The results reveal that the fluorinated dipole (-C-F bonds) alignment of the P(VDF-TrFE) at the semiconductor-dielectric interface was more favorable for hole accumulation and transport at the active channel than for electron accumulation and transport.<sup>27</sup> The high-performance complementary inverters had voltage gains of more than 25, an ideal inverting voltage ( $V_{inv}$ ) of nearly half of the supplied bias ( $1/2 V_{DD}$ ), a high noise immunity of ~75% of the ideal value ( $1/2 V_{DD}$ ), and low-voltage operation down to 2 V at the 7:3 blend ratio.

#### RESULTS AND DISCUSSION

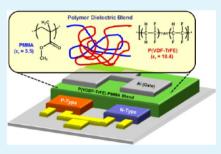

**High-k Blended Dielectrics.** In this study, we used highperformance p- and n-type polymer semiconductors, PC12TV12T and P(NDI2OD-T2), respectively, the molecular structures of which are shown in Figure 1b. The spin-coated

Figure 1. Molecular structures of (a) PMMA and P(VDF-TrFE) polymer gate dielectrics and (b) P(NDI2OD-T2) and PC12TV12T polymer semiconductors. (c) TG/BC OFET device structure and CCD camera image of the inkjet-printed PC12TV12T active feature.

staggered PC12TV12T and P(NDI2OD-T2) showed high  $\mu_{\text{FET}}$ values of more than 1.0  $\text{cm}^2/(\text{V s})$  and 0.2–0.85  $\text{cm}^2/(\text{V s})$  with PMMA and Au S/D electrodes, respectively.<sup>29,31</sup> To realize complementary ICs, the individual p- and n-channel semiconductor layers should be properly defined using costeffective printing methods such as inkjet printing. However, the printed active features commonly showed rough top-surface topologies with typical peak-to-valley roughnesses of a few tens of nanometers because of the coffee-stain effect.<sup>23,32</sup> It is important to obtain a flat semiconductor top surface, especially in TG OFETs, because most charge carriers are transported within a few semiconductor molecular layers at the semiconductor-dielectric interface, and the rough surface limits the thickness downscaling of the polymer gate dielectric layer.<sup>33</sup> Although there have been previous studies on solving the coffee-stain problem that looked at factors such as the careful choice of solvents and solution concentrations, substrate heating, and/or the use of a Marangoni flow, the film thickness and surface roughness of the printed features continue to limit our ability to control the surface morphology.34-36 In the

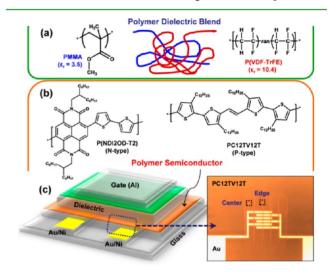

present study, as shown in Figure 2, inkjet-printed p- and ntype polymer semiconductors exhibited relatively rough

Figure 2. AFM images of the inkjet-printed PC12TV12T layer; (a, c) center and (b, d) edge regions, as represented in Figure 1c.

topologies, with peak-to-valley roughnesses of ~40 nm even after high-temperature thermal annealing (at 200 °C) for more than a few hours. Therefore, a thick enough high-*k* gate dielectric layers is imperative for the development of lowvoltage-operated TG OFETs and circuits using inkjet-printed conjugated molecules. In addition, although peak-to-valley roughness in the edge region of the inkjet-printed active feature is quite large of ~40 nm, surface roughness in the center region is very smooth with RMS roughness of ~0.35 nm, which is the same direction to the charge transport in our top-gated OFET devices. Therefore, it leads to relatively high mobilities of the inkjet-printed top-gated OFETs comparable to those of spincoated devices.

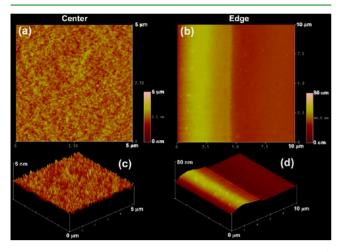

As shown by the atomic force microscopy (AFM) images in Figure 3, the PMMA and P(VDF-TrFE):PMMA blended dielectric films with blending ratios of 5:5, 7:3, and 9:1 showed amorphous film morphologies. Even the homogeneous P(VDF-TrFE) film exhibited no explicit crystalline morphology at a low annealing temperature (80 °C). It was noted that a 5:5 blend ratio induced a great deal of phase separation and a rough surface topology with a peak-to-peak deviation of more than 100 nm, presumably because it produces the highest mixing entropy between the two blended polymer components. However, when a small amount of PMMA (10-30 v/v %) was added to the P(VDF-TrFE) solution, no significant phase separation was induced, and a relatively smooth film morphology was produced (see Figure 3f). The high-kdielectric polymer P(VDF-TrFE) ( $\varepsilon_r = 10.4$  at 100 kHz) typically shows ferroelectric memory properties and thus produces a large hysteresis loop in transfer curves with forward and backward bias scans.<sup>37</sup> However, no significant bias hysteresis behavior was observed in this study after P(VDF-TrFE) was blended with the amorphous dielectric polymer PMMA (see Figure 5). The formation of the crystalline ferroelectric  $\beta$ -phase in the P(VDF-TrFE) film was efficiently suppressed by blending it with PMMA.<sup>25</sup> The polarization behavior of the P(VDF-TrFE) strongly depended on its crystallinity below its Curie temperature (~80 °C) and abruptly decreased when the film thickness was less than 100 nm because of a significant reduction in the degree of crystallization in the film.<sup>37</sup> Therefore, the relatively thin film thickness of the P(VDF-TrFE):PMMA blend dielectrics (200-250 nm) and the low degree of the crystallization due to the fast spin-casting and low-temperature processing (<80 °C, far below the melting

**Figure 3.** (a–e) AFM images of the (a) PMMA, (b) P(VDF-TrFE):PMMA = 5:5, (c) P(VDF-TrFE):PMMA = 7:3, (d) P(VDF-TrFE):PMMA = 9:1, and (e) P(VDF-TrFE) film surfaces (tapping mode, 5  $\mu$ m × 5  $\mu$ m scan area). (f) Film roughness profiles of the PMMA, P(VDF-TrFE):PMMA = 5:5, P(VDF-TrFE):PMMA = 7:3, and P(VDF-TrFE):PMMA = 9:1 gate dielectric surfaces.

point at 140–160  $^{\circ}C)$  presumably led to the negligible ferroelectric memory behavior.  $^{37,38}$

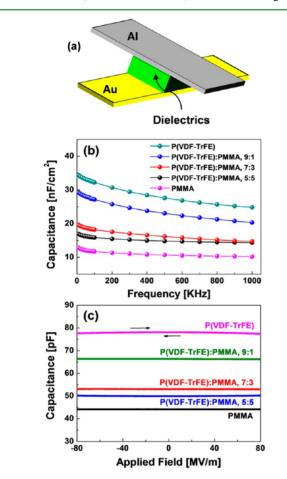

The capacitance characteristics were studied on a metal(Au)/ insulator/metal(Al) structure for PMMA (~250 nm thick), P(VDF-TrFE) (~260 nm thick), and P(VDF-TrFE):PMMA blend dielectrics (250–260 nm thick), as shown in Figure 4a.

Figure 4. (a) Diode structure used to obtain the capacitance characteristics of the polymer gate dielectrics. (b) Capacitance vs frequency (at an applied voltage of 10 V) and (c) capacitance vs applied voltage (at an applied frequency of 100 kHz) characteristics of the PMMA, P(VDF-TrFE), and P(VDF-TrFE):PMMA blends with blend ratios of 5:5, 7:3, and 9:1.

As the capacitance-frequency (C-F) characteristics show (Figure 4b), bare P(VDF-TrFE) and bare PMMA films had the highest and lowest  $C_i [\varepsilon_r]$  values at 10 kHz, ~35 nF/cm<sup>2</sup> [10.4] and ~12.5 nF/cm<sup>2</sup> [3.6], respectively. The C<sub>i</sub> [ $\varepsilon_r$ ] decreased to  $\sim 30 \text{ nF/cm}^2$  [8.4],  $\sim 20 \text{ nF/cm}^2$  [5.9], and  $\sim 17$  $nF/cm^{2}$  [5.3] when the PMMA concentration in the P(VDF-TrFE):PMMA blend dielectric was increased to 10, 30, and 50 v/v %, respectively. The C<sub>i</sub> value also decreased with frequency, as expected, because the dipole alignment in high-k dielectrics limits the polarization response time.<sup>39</sup> However, C<sub>i</sub> did not decrease critically with the frequency and was still >20  $nF/cm^2$ at high frequency (1 MHz). The  $C_i$  reached >60 nF/cm<sup>2</sup> at 1 MHz when the dielectric film thickness was decreased to ~80 nm (not shown here). The capacitance-voltage (C-V)characteristics were measured at 100 kHz. As shown in Figure 4c, when the forward and backward bias was scanned up to  $\sim 80$ MV/m, no significant ferroelectric behavior was exhibited in any of the C-V curves.<sup>25,26</sup> It should be noted that typical

ferroelectric P(VDF-TrFE) films show a coercive electric field of approximately  $\sim$ 50 MV/m.<sup>38</sup> Therefore, the pure P(VDF-TrFE) and P(VDF-TrFE):PMMA blend dielectrics showed no pronounced ferroelectric properties.

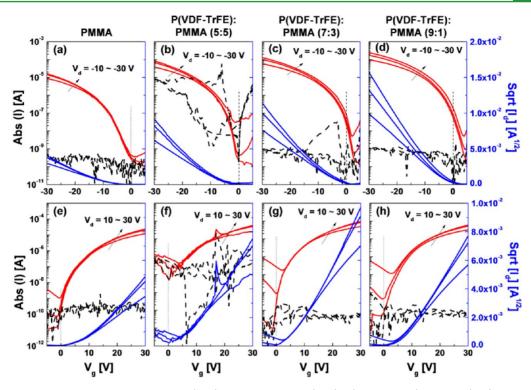

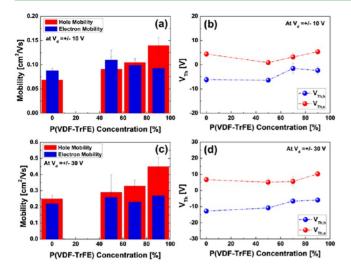

Organic Field-Effect Transistor Characteristics. Staggered TG/BC OFET devices were fabricated using the P(VDF-TrFE):PMMA blend dielectrics with blend ratios of 5:5, 7:3, and 9:1. Figure 5 shows the transfer characteristics of the inkjetprinted PC12TV12T (p-type) and P(NDI2OD-T2) (n-type) OFET devices with various gate dielectric layers at drain voltages  $(V_d)$  of  $\pm 10$ ,  $\pm 20$ , and  $\pm 30$  V. The fundamental electrical parameters of the OFETs, namely,  $\mu_{\text{FET}}$ ,  $V_{\text{Th}}$ , and the on/off-current ratio  $(I_{on}/I_{off})$ , were obtained using the gradual channel approximation in the saturation region,  $V_{\rm d} = \pm 10 \text{ V}$ and  $\pm 30 V_{r}^{1130}$  as listed in Table 1. As shown in Figures 5 and 6, the p-channel (PC12TV12T) OFET properties were greatly enhanced, by as much as a factor of 2, whereas the n-channel (P(NDI2OD-T2)) OFET characteristics were changed only negligibly or became slightly worse as the concentration of P(VDF-TrFE) versus PMMA in the blended dielectrics increased. The initial hole  $(\mu_{\text{FET,h}})$  and electron mobilities  $(\mu_{\text{FET},e})$  of the PC12TV12T [or P(NDI2OD-T2)] OFETs with PMMA were ~0.069 [0.25] cm<sup>2</sup>/(V s) and 0.088 [0.22] cm<sup>2</sup>/ (V s), respectively, at  $V_d = \pm 10$  V [at  $V_d = \pm 30$  V], but  $\mu_{\text{FET,h}}$ and  $\mu_{\text{FET,e}}$  changed to 0.14 [0.45] cm<sup>2</sup>/(V s) and 0.093 [0.27]  $\text{cm}^2/(\text{V s})$ , respectively, at  $V_d = \pm 10 \text{ V}$  [at  $V_d = \pm 30 \text{ V}$ ] when the blended dielectrics with a P(VDF-TrFE):PMMA ratio of 9:1 were used. The V<sub>Th</sub> values of both p- and n-type OFETs were slightly shifted in the negative direction as the P(VDF-TrFE) concentration in the P(VDF-TrFE):PMMA blends increased from 10 v/v % to 50 v/v %.

The enhancement of the p-type OFET characteristics can be mainly understood as an effect of the dipoles in P(VDF-TrFE) in the blended dielectric layer. The fluorinated P(VDF-TrFE) has a number of -C-F dipoles unsymmetrically distributed in the polymer chain, and those dipoles can enhance the accumulation of positive charges (holes) at the semiconductor-dielectric interface, thereby pulling up the highest occupied molecular orbital (HOMO) and the lowest unoccupied molecular orbital (LUMO) levels of the semiconductors.<sup>27,40</sup> Therefore, the preferred accumulation of holes at the interface between the PC12TV12T semiconductor and P(VDF-TrFE) dielectrics efficiently enhances hole injection from the S/D electrodes and transport though the active channel, which can be seen as the higher  $\mu_{\rm FET,h}$  in the blended dielectrics with higher concentrations of P(VDF-TrFE) as compared to PMMA hydrogenated (-C-H) dielectric devices. However, the destructive effect of the fluorinated dipoles in P(VDF-TrFE) depletes the electrons from the active channel of the n-type P(NDI2OD-T2) OFETs, thereby decreasing  $\mu_{\text{FET},e}$  and positively shifting the  $V_{\text{Th,e}}$ . In contrast, the PMMA dielectric devices had a high  $\mu_{\rm FET,e}$  and a slightly negative onset voltage, which can be attributed to the efficient accumulation of electrons at the semiconductor-dielectric interface due to the pulled-down HOMO and LUMO levels. The deterioration of the n-type P(NDI2OD-T2) OFET properties due to electron depletion was much more severe for pure P(VDF-TrFE) than for the P(VDF-TrFE):PMMA blends, which presumably induced more moderate effects between the PMMA and P(VDF-TrFE) materials.

The effect of the fluorinated high-k dielectrics is very similar to the channel carrier modulation (accumulation of holes and depletion of electrons) produced by fluorinated SAMs, as

**Figure 5.** Transfer characteristics of the inkjet-printed (a–d) PC12TV12T and (e–h) P(NDI2OD-T2) OFETs: (a, e) PMMA-only layer and P(VDF-TrFE):PMMA blends with blend ratios of (b, f) 5:5, (c, g) 7:3, and (d, h) 9:1, respectively. Red solid, black dashed, and blue solid lines indicate the drain current ( $I_d$ ), gate leakage current ( $I_g$ ), and sqrt( $I_d$ ) at  $V_d = \pm 10, \pm 20$ , and  $\pm 30$  V, respectively.

Table 1. Fundamental Parameters of OFET Devices Using Various Polymer TG Dielectrics: a PMMA Single Layer and P(VDF-TrFE):PMMA blends with Various Ratios from 5:5 to 9:1 (Au/Ni S/D electrode, W/L = 1 mm/20  $\mu$ m)

|                           |                                | at $V_{\rm d} = \pm 10 \ {\rm V}$                     |                       |                          | at $V_{\rm d} = \pm 30 \text{ V}$         |                       |                          |

|---------------------------|--------------------------------|-------------------------------------------------------|-----------------------|--------------------------|-------------------------------------------|-----------------------|--------------------------|

| semiconductor             | dielectric                     | $\frac{\mu_{\text{FET}}}{(\text{cm}^2/(\text{V s}))}$ | $V_{\mathrm{Th}}$ (V) | $I_{\rm on}/I_{\rm off}$ | $(\mathrm{cm}^2/(\mathrm{V} \mathrm{s}))$ | $V_{\mathrm{Th}}$ (V) | $I_{\rm on}/I_{\rm off}$ |

| PC12TV12T (p-type)        | PMMA                           | 0.069 (±0.0065)                                       | $-6.17 (\pm 1.31)$    | $\sim 1 \times 10^5$     | 0.25 (±0.021)                             | $-12.74(\pm 1.47)$    | $\sim 1 \times 10^{6}$   |

|                           | P(VDF-TrFE):PMMA blend,<br>5:5 | 0.091 (±0.039)                                        | -6.35 (±0.22)         | $\sim 5 \times 10^{5}$   | 0.29 (±0.11)                              | -10.75 (±1.21)        | $\sim 1 \times 10^{3}$   |

|                           | P(VDF-TrFE):PMMA blend,<br>7:3 | 0.105 (±0.0082)                                       | -1.50 (±1.99)         | $\sim 5 \times 10^{5}$   | 0.33 (±0.036)                             | -6.50 (±1.38)         | $\sim 5 \times 10^{5}$   |

|                           | P(VDF-TrFE):PMMA blend,<br>9:1 | 0.14 (±0.016)                                         | -2.34 (±1.48)         | $\sim 1 \times 10^{6}$   | 0.45 (±0.056)                             | -5.90 (±0.92)         | $\sim 5 \times 10^4$     |

| P(NDI2OD-T2) (n-<br>type) | PMMA                           | $0.088 (\pm 0.0046)$                                  | 4.43 (±0.85)          | $\sim 5 \times 10^4$     | 0.22 (±0.010)                             | 6.80 (±0.71)          | $\sim 1 \times 10^5$     |

|                           | P(VDF-TrFE):PMMA blend,<br>5:5 | 0.11 (±0.0058)                                        | 0.90 (±0.46)          | $\sim 1 \times 10^4$     | 0.26 (±0.036)                             | 5.15 (±1.99)          | $\sim 1 \times 10^{3}$   |

|                           | P(VDF-TrFE):PMMA blend,<br>7:3 | 0.10 (±0.011)                                         | 3.25 (±1.20)          | $\sim 1 \times 10^{4}$   | 0.23 (±0.012)                             | 5.67 (±2.92)          | $\sim 1 \times 10^{3}$   |

|                           | P(VDF-TrFE):PMMA blend,<br>9:1 | 0.093 (±0.0059)                                       | 5.37 (±0.21)          | $\sim 5 \times 10^4$     | 0.27 (±0.016)                             | 10.30 (±0.56)         | $\sim 1 \times 10^3$     |

reported by Kobayashi et al..<sup>28</sup> In addition, G. Gelinck et al., reported similar results in polymer light emitting transistors with ferroelectric polymers as gate dielectrics.<sup>41</sup> We can finally achieve high, well-balanced  $\mu_{\rm FET,e}$  and  $\mu_{\rm FET,h}$  values under relatively low-voltage operation (at  $V_{\rm d} = \pm 10$  V) by the proper selection of the concentrations of P(VDF-TrFE) and PMMA. The  $V_{\rm Th,h}$  and  $V_{\rm Th,e}$  values were also relatively small, below 4 V, for a specific blend composition, i.e., a 7:3 blend ratio between P(VDF-TrFE) and PMMA (see Figure 6a). In addition, the modulation of the OFET characteristics by P(VDF-TrFE) has been generally observed for most p- and n-channel OFETs as well as for ambipolar polymer semiconductors including poly(3-hexylthiophene) (P3HT) and poly[(9,9-dioctylfluorenyl-2,7-diyl)-co-(bithiophene)] (F8T2), poly(9,9-dioctylfluore ene-co-benthiadiazole) (F8BT), and poly(thienlylenevinyleneco-phthalimide) (PTVPhI-Eh).<sup>27</sup>

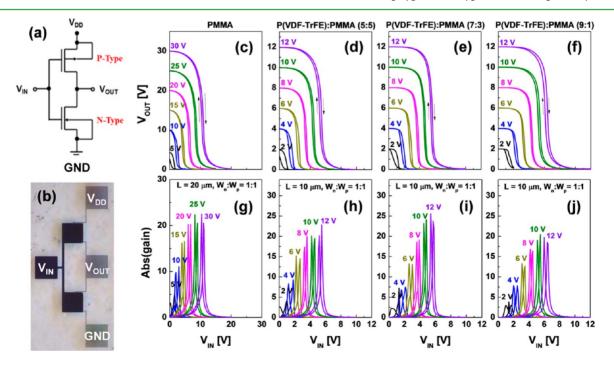

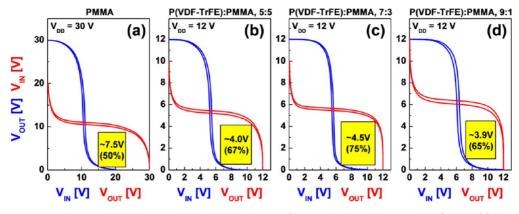

**Complementary Inverters.** The P(VDF-TrFE):PMMA blend dielectrics were used to fabricate low-voltage-operating complementary inverter circuits. The complementary inverters consisted of p-type [PC12TV12T] and n-type [P(NDI2OD-T2)] OFETs (see Figure 7a, b) in which the p- and n-type semiconductor areas were defined using the inkjet-printing method. Figure 7 shows the voltage transfer characteristics (VTCs; panels c-f) and the corresponding voltage gains (panels g-j) of the complementary inverters (channel width/length ratio  $W_p/L_p = W_n/L_n = 1 \text{ mm}/20 \ \mu\text{m}$ ) at various  $V_{\text{DD}}$  values from 2 to 30 V with PMMA and P(VDF-TrFE):PMMA blends at blend ratios of 5:5, 7:3, and 9:1. As shown in panels c

**Figure 6.** (a, c) Field-effect mobility and (b, d) threshold voltage ( $V_{Th}$ ) of the PC12TV12T [p-type] and P(NDI2OD-T2) [n-type] OFETs (a, b) at  $V_d = \pm 10$  V and (c, d) at  $V_d = \pm 30$  V, respectively, with PMMA and P(VDF-TrFE):PMMA polymer blend dielectric layers at various P(VDF-TrFE) concentrations from 50 to 90 wt %.

and g in Figure 7, the inverters with PMMA dielectrics required an operation voltage more than two times higher than required for the other dielectrics. The inverting voltage ( $V_{inv}$ ) and DC voltage gains of the PMMA devices were ~11 V and ~22, respectively, at  $V_{DD} = 30$  V. The  $V_{inv}$  of the complementary inverter is reached when both the p- and n-channel OFETs are operating in the saturation region<sup>8</sup> and can be expressed by eq 1

$$V_{\rm inv} = \frac{V_{\rm DD} + V_{\rm Th}^{\rm p} + V_{\rm Th}^{\rm n} \sqrt{\frac{\rho_{\rm n}}{\beta_{\rm p}}}}{1 + \sqrt{\frac{\beta_{\rm n}}{\beta_{\rm p}}}}$$

(1)

0

where  $\beta = (W/L)\mu_{\text{FET}}C_i$  is a design factor for adjusting the pand n-channel currents of the transistors and the superscripts p and n denote the semiconductor type.<sup>8</sup> The  $V_{inv}$  of the PMMA device was slightly shifted in the negative direction, by  $\sim 4$  V, from the theoretical ideal position at 1/2  $V_{\text{DD}}$ . This was attributed to the higher  $\mu_{\mathrm{FET,e}}$  and smaller  $V_{\mathrm{Th,e}}$  of the P(NDI2OD-T2) OFETs than those of PC12TV12T OFETs using PMMA dielectrics, since the other parameters, such as  $V_{\rm DD}$ , W/L, and  $C_{\rm i}$ , were equal in both p- and n-type OFETs. Therefore, when a PMMA dielectric is applied, the factor  $\beta$ must be carefully chosen to optimize the performance of the complementary circuits. It becomes a critical parameter, in particular, for highly complicated ICs and is typically determined by changing the W/L of the S/D electrode once the p- and n-type semiconductors and gate dielectrics are fixed.<sup>8</sup> The complementary inverters using P(VDF-TrFE):PMMA blend dielectrics operated at a low voltage, down to  $\sim 2$  V, compared favorably to PMMA devices (see Figure 7). Moreover, the inverter characteristics such as the VTCs and gains were systematically controllable by changing the blend ratio from 5:5 to 7:3 to 9:1. As shown in panels e and i in Figure 7, the 7:3 blend ratio showed the most optimized inverter characteristics, such as an ideal  $V_{\mathrm{inv}}$  near  $1/2~V_{\mathrm{DD}}$  and a high gain of more than 25, because of its well-balanced high pand n-channel OFET characteristics under low-voltage conditions ( $V_d = \pm 10$  V) [the  $\mu_{\text{FET},e}$  ( $V_{\text{Th},e}$ ) and  $\mu_{\text{FET},h}$  $(V_{\rm Th,h})$  were ~0.1 cm<sup>2</sup>/(V s) (3.25 V) and ~0.095 cm<sup>2</sup>/(V s) (-1.5 V) for p-type and n-type OFETs, respectively.

**Figure 7.** Complementary inverter characteristics under various  $V_{DD}$  conditions from 2 to 30 V (p-type is PC12TV12T and n-type is P(NDI2OD-T2),  $W_p/L_p = W_n/L_n = 1 \text{ mm/10 } \mu\text{m}$ ). (a) Circuit configuration and (b) a CCD camera image of the fabricated complementary inverter. (c-f) Voltage transfer characteristics (VTCs) and (g-j) corresponding voltage gains of the complementary inverters at  $V_{DD} = 30$  or 12 V using (c, g) a PMMA-only layer and P(VDF-TrFE):PMMA blend dielectrics with blend ratios of (d, h) 5:5, (e, i) 7:3, and (f, j) 9:1.

**Figure 8.** Noise margins at  $V_{DD}$  = 30 or 12 V of the complementary inverters ( $W_p/L_p = W_n/L_n = 1 \text{ mm}/10 \mu \text{m}$ ) using (a) PMMA-only layer and P(VDF-TrFE):PMMA blend dielectrics with blend ratios of (b) 5:5, (c) 7:3, and (d) 9:1.

Figure 8 shows the noise margins (NMs) of the complementary inverters ( $W_p/L_p = W_n/L_n = 1 \text{ mm}/20 \mu \text{m}$ ) with PMMA (Figure 8a) and P(VDF-TrFE):PMMA blends (Figures 8b-d) at blend ratios of 5:5, 7:3, and 9:1 at  $V_{\text{DD}} = 30 \text{ V}$  (for PMMA) or 12 V (for the blend dielectrics). As shown in Figure 8, the P(VDF-TrFE):PMMA devices had much better NMs than the PMMA device. The PMMA inverter device had the lowest NM of only 50%, whereas the 7:3 blend ratio produced the largest NM of as high as 75% of theoretical value ( $1/2 V_{\text{DD}}$ ). The NMs of digital logic gates or circuits indicate how well the circuit will perform under noisy conditions.<sup>8</sup> The NM is given by eq 2, as follows

$$V_{\rm IH} - V_{\rm IL} = -\frac{(V_{\rm OH} - V_{\rm OL})}{g} = -\frac{V_{\rm DD}}{g}$$

$$V_{\rm IH} = V_{\rm M} - \frac{V_{\rm M}}{g}$$

$$V_{\rm IL} = V_{\rm M} + \frac{V_{\rm DD} - V_{\rm M}}{g}$$

$$NM_{\rm H} = V_{\rm OH} - V_{\rm IH} = V_{\rm DD} - V_{\rm IH}$$

$$NM_{\rm L} = V_{\rm IL} - V_{\rm OL} = V_{\rm IL}$$

where  $NM_H$  and  $NM_L$  are the noise margins for the high (H) and low (L) logic levels and  $V_{OH}$ ,  $V_{IH}$ ,  $V_{IL}$ , and  $V_{OL}$  are the output voltages  $(V_{\rm O})$  and input voltages  $(V_{\rm I})$  at the high (H) and low (L) logic levels. By definition,  $V_{\rm IH}$  and  $V_{\rm IL}$  are the operational points of the inverter at which  $d(V_{OUT})/d(V_{IN}) =$ -1. From eq 2, it is obvious that a high gain (g) at the switching threshold  $(V_{\rm M})$  in the transition region  $(V_{\rm H}-V_{\rm H})$  is very desirable for obtaining high noise immunity.<sup>8</sup> Figures 8ad reveal that the inverters with P(VDF-TrFE):PMMA blends showed more than 25% higher NMs than those with PMMA, and the 7:3 ratio produced a ~10% improvement in NM compared to the other blend ratios, because those inverters had the highest voltage gains at nearly the ideal  $V_{\rm M}$  position near 1/ 2  $V_{\rm DD}$  and small bias hysteresis during forward and reverse  $V_{\rm IN}$ scans. The complementary inverter characteristics could also be optimized by simply changing the blend ratio of the blended gate dielectrics, which led to different mobilities and  $V_{Th}$  values of the p- and n-type OFETs.

The fluorinated high-*k* dielectric P(VDF-TrFE) is used a variety of applications such as in acoustic transducers, electromechanical actuators, heat sensors, and ferroelectric memory.<sup>42–44</sup> These materials have also been used in organic

FETs to reduce the operating voltage.<sup>25,45</sup> These applications mainly utilized the unique properties, i.e., the pyroelectric and piezoelectric responses and permanent electric polarization, arising from the permanent -C-F dipoles of P(VDF-TrFE). Furthermore, as shown in this study, the functionality of the -C-F dipoles can be utilized to tune the channel charge transport of p-type and n-type unipolar or ambipolar semiconductors.<sup>27</sup> This approach is similar to the continuous tuning of  $V_{\text{Th}}$ , which can be facilitated by employing gate dielectrics  $(Al_2O_x)$  that are based on mixed alkyl/fluoroalkyl phosphonic acid SAMs.<sup>46</sup> The V<sub>Th</sub> of the OFETs was a linear function of the atomic fluorine concentration in the mixed SAM dielectric with a modulation coefficient of 40 mV/%.<sup>46</sup> Although the mixed alkyl/fluoroalkyl SAMs were successfully utilized to fabricate high-performance complementary organic circuitry,<sup>46</sup> the SAM method is limited in that it can only be applied to specific dielectric surfaces, such as SiO<sub>2</sub> for silane SAMs and Al<sub>2</sub>O<sub>x</sub> for phosphonic acid SAMs. In contrast, our methods for controlling the charge transport using fluorinated high-k polymer dielectric blends can be utilized generally, regardless of the dielectric surface and on any other substrate, such as on glass or plastic. We believe that this approach would be a promising methodology for the development of highperformance complementary metal oxide semiconductor (CMOS)-based printed organic integrated circuits and can be used to broaden the applications of ambipolar materials in complementary-like circuits.

#### CONCLUSIONS

We have demonstrated high-performance TG/BC OFETs and their complementary electronic circuits using inkjet-printed conjugated polymers and high-k polymer dielectric blends of P(VDF-TrFE) and PMMA. The high-k polymer dielectric blends enable the fabrication of well-balanced CMOS inverters with controlled hole and electron transport and low-voltage operation due to the high dielectric constant. Both PC12TV12T (p-channel) and P(NDI2OD-T2) (n-channel) inkjet-printed OFETs showed high  $\mu_{\rm FET}$  values, reaching 0.45 and 0.27  $\text{cm}^2/(\text{V s})$ , respectively. Importantly, the p-type OFETs characteristics were gradually enhanced in proportion to the P(VDF-TrFE) concentration in the dielectric blends, while n-type properties were slightly degraded or not significantly changed. It was explained that the fluorinated dipole (-C-F bonds) alignment of the P(VDF-TrFE) at the semiconductor-dielectric interface was more favorable for hole accumulation and transport at the active channel rather than for

(2)

electron accumulation and transport. Therefore, high, wellbalanced electron and hole mobilities and good  $V_{\rm Th}$  values were obtained at a 7:3 blend ratio between P(VDF-TrFE) and PMMA. When the optimized blended dielectrics were used, high-performance complementary inverters were demonstrated with a voltage gain of more than 25, an ideal inverting voltage  $(V_{\rm inv})$  near 1/2  $V_{\rm DD}$ , a high noise immunity of ~75% of 1/2  $V_{\rm DD}$ , and low-voltage operation down to 2 V.

## EXPERIMENTAL METHODS

Field-Effect Transistor and Inverter Fabrication. Corning Eagle 2000 glass substrates were cleaned sequentially in an ultrasonic bath with deionized water, acetone, and isopropanol for 10 min each. The Au/Ni (15 nm/3 nm thick) patterns used for the S/D electrodes were fabricated using a conventional lift-off photolithography procedure. The p-type polymer semiconducting material, PC12TV12T, was synthesized in our laboratory using a previously published procedure,<sup>29</sup> and P(NDI2OD-T2) (ActivInk N2200) was supplied by the Polyera Corporation and used as received. PC12TV12T and P(NDI2OD-T2) were dissolved in anhydrous pxylene to obtain an approximately 5 mg/mL solution. The semiconductor inks were inkjet-printed using a piezoelectric-type single nozzle with an orifice 50  $\mu$ m in diameter (Microfab, Inc.) and a custom-built inkjet printing machine (UJ 200, Unijet, Inc.) in air. The inkjet-patterned semiconductor films were thermally annealed at 200 °C for 30 min in a N<sub>2</sub>-purged glovebox. PMMA (Aldrich, MW = 120 kD) and P(VDF-TrFE) (Solvay, 70:30 molar ratio, random copolymer) were used as dielectric materials without further purification. PMMA (70 mg/mL) and P(VDF-TrFE) (70 mg/mL) were dissolved in dimethyl sulphoxide (DMSO) and mixed with 5:5, 7:3, and 9:1 blend ratios. The PMMA and P(VDF-TrFE):PMMA blend dielectric solutions were spin-coated at ~5000 rpm in a N2purged glovebox. After dielectric layer coating, the devices were baked at 80 °C for more than 2 h in N2 to completely remove residual solvents. The transistors were completed by depositing the TG electrodes (Al) via thermal evaporation using a metal shadow mask.

Thin Film and Device Characterization. The OFET electrical characteristics and the static characteristics of the complementary inverters were measured using a Keithley 4200-SCS in a N<sub>2</sub>-filled glovebox. The  $\mu_{\text{FET}}$  and V<sub>Th</sub> values were calculated in the saturation region using the gradual channel approximation equations.<sup>30</sup> The C–F characteristics were measured using a built-in Keithley 4200-SCS CV setup starting from 10 kHz to a 1 MHz frequency. The C–V characteristics were measured using an Agilent 4284A precision LCR meter and a Keithley 4200-SCS at a frequency of 100 kHz. The surface profiles were measured using a surface profiler (Ambios, XP-1) after inkjet-printing of the P(NDI2OD-T2) and thermal annealing at 200 °C for 30 min, or after spin-coating and thermal baking of the gate dielectric layers. The surface morphology of the gate dielectric films was investigated via tapping-mode AFM (Nanoscope III, Veeco Instruments, Inc.) at the Korea Basic Science Institute (KBSI).

## AUTHOR INFORMATION

### **Corresponding Author**

\*E-mail: yynoh@hanbat.ac.kr.

#### Present Address

<sup>‡</sup>Department of Chemistry, Northwestern University, 2145 Sheridan Rd., Evanston, IL 60208, USA

#### Notes

The authors declare no competing financial interest.

# ACKNOWLEDGMENTS

This research was financially supported by a grant (code 2011-0031639) from the Center for Advanced Soft Electronics under the Global Frontier Research Program of the Ministry of Education, Science and Technology, Korea, and a grant from the Basic Science Research Program through the National Research Foundation of Korea (NRF), funded by the Ministry of Education, Science and Technology (MEST) (2010-0023180).

## REFERENCES

(1) Gelinck, G.; Heremans, P.; Nomoto, K.; Anthopoulos, T. D. Adv. Mater. 2010, 22, 3778–3798.

(2) Chen, P.; Fu, Y.; Aminirad, R.; Wang, C.; Zhang, J.; Wang, K.; Galatsis, K.; Zhou, C. *Nano Lett.* **2011**, *11*, 5301–5308.

(3) Usta, H.; Facchetti, A.; Marks, T. J. Acc. Chem. Res. 2011, 44, 501-510.

(4) Kim, S.-S.; Na, S.-I.; Jo, J.; Tae, G.; Kim, D.-Y. Adv. Mater. 2007, 19, 4410–4415.

(5) Baeg, K.-J.; Noh, Y.-Y.; Ghim, J.; Kang, S.-J.; Lee, H.; Kim, D.-Y. *Adv. Mater.* **2006**, *18*, 3179–3183.

(6) Baeg, K.-J.; Khim, D.; Kim, J.; Yang, B.-D.; Kang, M.; Jung, S.-W.; You, I.-K.; Kim, D.-Y.; Noh, Y.-Y. *Adv. Funct. Mater.* **2012**, *22*, 2915–2926.

(7) Kola, S.; Sinha, J.; Katz, H. E. J. Polym. Sci., Part B: Polym. Phys. **2012**, 50, 1090–1120.

(8) Rabaey, J. M.; Chandrakasan, A.; Nikolić, B. In *Digital Integrated Circuits*, 2nd ed.; Prentice Hall: Upper Saddle River, NJ, 2003; Vol. *5*, p 177.

(9) Baeg, K.-J.; Khim, D.; Kim, D.-Y.; Jung, S.-W.; Koo, J. B.; You, I.-K.; Yan, H.; Facchetti, A.; Noh, Y.-Y. J. Polym. Sci., Part B: Polym. Phys. 2011, 49, 62–67.

(10) Rogers, J. A.; Someya, T.; Huang, Y. Science **2010**, 327, 1603–1607.

(11) Facchetti, A. Chem. Mater. 2011, 23, 733-758.

(12) Katz, H. E. Chem. Mater. 2004, 16, 4748-4756.

(13) Klauk, H.; Zschieschang, U.; Pflaum, J.; Halik, M. Nature 2007, 445, 745–748.

(14) Crone, B.; Dodabalapur, A.; Lin, Y.-Y.; Filas, R. W.; Bao, Z.; LaDuca, A.; Sarpeshkar, R.; Katz, H. E.; Li, W. *Nature* **2000**, *403*, 521–523.

(15) Cho, J. H.; Lee, J.; Xia, Y.; Kim, B. S.; He, Y.; Renn, M. J.; Lodge, T. P.; Frisbie, C. D. *Nat. Mater.* **2008**, *7*, 900–906.

(16) Fix, W.; Ullmann, A.; Ficker, J.; Clemens, W. Appl. Phys. Lett. 2002, 81, 1735–1737.

(17) Baeg, K.-J.; Kim, J.; Khim, D.; Caironi, M.; Kim, D.-Y.; You, I.-K.; Quinn, J. R.; Facchetti, A.; Noh, Y.-Y. ACS Appl. Mater. Interfaces **2011**, *3*, 3205–3214.

(18) Knobloch, A.; Manuelli, A.; Bernds, A.; Clemens, W. J. Appl. Phys. 2004, 96, 2286-2291.

(19) Ante, F.; Kälblein, D.; Zaki, T.; Zschieschang, U.; Takimiya, K.; Ikeda, M.; Sekitani, T.; Someya, T.; Burghartz, J. N.; Kern, K.; Klauk, H. *Small* **2012**, *8*, 73–79.

(20) Richards, T. J.; Sirringhaus, H. J. Appl. Phys. 2007, 102, 094510-1-094510-6.

(21) Noh, Y.-Y.; Zhao, N.; Caironi, M.; Sirringhaus, H. Nat. Nanotechnol. 2007, 2, 784–789.

(22) Yunker, P. J.; Still, T.; Lohr, M. A.; Yodh, A. G. Nature 2011, 476, 308-311.

(23) Voigt, M. M.; Guite, A.; Chung, D.-Y.; Khan, R. U. A.; Campbell, A. J.; Bradley, D. D. C.; Meng, F.; Steinke, J. H. G.; Tierney, S.; McCulloch, I.; Penxten, H.; Lutsen, L.; Douheret, O.; Manca, J.; Brokmann, U.; Sönnichsen, K.; Hülsenberg, D.; Bock, W.; Barron, C.; Blanckaert, N.; Springer, S.; Grupp, J.; Mosley, A. *Adv. Funct. Mater.* **2010**, *20*, 239–246.

(24) Lee, K. H.; Lee, G.; Lee, K.; Oh, M. S.; Im, S.; Yoon, S.-M. Adv. Mater. 2009, 21, 4287–2491.

(25) Jung, S.-W.; Baeg, K.-J.; Yoon, S.-M.; You, I.-K.; Lee, J.-K.; Kim, Y.-S.; Noh, Y.-Y. J. Appl. Phys. **2010**, 108, 102810–1–102810–5.

(26) Jung, S.-W.; Yoon, S.-M.; Kang, S. Y.; You, I.-K.; Koo, J. B.; Baeg, K.-J.; Noh, Y.-Y. *Curr. Appl. Phys.* **2011**, *11*, S213–S218.

(27) Baeg, K.-J.; Khim, D.; Jung, S. W.; Kang, M.; You, I.-K.; Kim, D.-Y.; Facchetti, A.; Noh, Y.-Y. *Adv. Mater.* **2012**, *24*, 5433–5439. (28) Kobayashi, S.; Nishikawa, T.; Takenobu, T.; Mori, S.; Shimoda, T.; Mitani, T.; Shimotani, H.; Yoshimoto, N.; Ogawa, S.; Iwasa, Y. *Nat. Mater.* **2004**, *3*, 317–322.

- (29) Kim, J.; Lim, B.; Baeg, K.-J.; Noh, Y.-Y.; Khim, D.; Jeong, H.-G.; Yun, J.-M.; Kim, D.-Y. *Chem. Mater.* **2011**, *23*, 4663–4665.

- (30) Sze, S. M. In *Physics of Semiconductor Devices*, 2nd ed.; Wiley-Interscience: Hoboken, NJ, 1981; Vol. 8, p 438.

(31) Yan, H.; Chen, Z.; Zheng, Y.; Newman, C.; Quinn, J. R.; Dötz, F.; Kastler, M.; Facchetti, A. *Nature* **2009**, 457, 679–686.

(32) Deegan, R. D.; Bakajin, O.; Dupont, T. F.; Huber, G.; Nagel, S. R.; Witten, T. A. *Nature* **1997**, 389, 827–829.

(33) Sirringhaus, H.; Bird, M.; Zhao, N. Adv. Mater. 2010, 22, 3893–3898.

(34) Soltman, D.; Subramanian, V. Langmuir 2008, 24, 2224-2231.

(35) Hu, H.; Larson, R. G. J. Phys. Chem. B 2006, 110, 7090-7094.

(36) Lim, J. A.; Lee, W. H.; Lee, H. S.; Lee, J. H.; Park, Y. D.; Cho, K. Adv. Funct. Mater. 2008, 18, 229–234.

(37) Park, Y. J.; Kang, S. J.; Lotz, B.; Brinkmann, M.; Thierry, A.; Kim, K. J.; Park, C. *Macromolecules* **2008**, *41*, 8648–8654.

(38) Park, Y. J.; Kang, S. J.; Park, C.; Kim, K. J.; Lee, H. S.; Lee, M. S.; Chung, U.-I.; Park, I. J. *Appl. Phys. Lett.* **2006**, *88*, 242908–1– 242908–3.

(39) Livingston, J. D. In *Electronic Properties of Engineering Materials*; Wiely-Interscience: New York, 1999; Vol. 3, p 39.

(40) Chung, Y.; Verploegen, E.; Vailionis, A.; Sun, Y.; Nishi, Y.; Murmann, B.; Bao, Z. *Nano Lett.* **2011**, *11*, 1161–1165.

(41) Li, X.; van Breemen, A. J. J. M.; Khikhlovskyi, V.; Smits, E. C. P.; Kemerink, M.; Broer, D. J.; Gelinck, G. H. Org. Electron. **2012**, *13*, 1742–1749.

(42) Lovinger, A. J. Science 1983, 220, 1115-1121.

(43) Zirk, M.; Sawatdee, A.; Helbig, U.; Krause, M.; Scheipl, G.; Kraker, E.; Ersman, P. A.; Nilsson, D.; Platt, D.; Bodö, P.; Bauer, S.; Domann, G.; Stadlober, B. *Adv. Mater.* **2011**, *23*, 2069–2074.

(44) Naber, R. C. G.; Tanase, C.; Blom, P. W. M.; Gelinck, G. H.; Marsman, A. W.; Touwslager, F. J.; Setayesh, S.; Leeuw, D. M. *Nat. Mater.* **2005**, *4*, 243–248.

(45) Li, J.; Sun, Z.; Yan, F. Adv. Mater. 2012, 24, 88-93.

(46) Zschieschang, U.; Ante, F.; Schlörholz, M.; Schmidt, M.; Kern, K.; Klauk, H. *Adv. Mater.* **2010**, *22*, 4489–4493.